Cmos Vlsi Vtu Notes Cbcs

VLSI design Book Latest Material Links Unit 1 Link – Unit 2 Link – Unit 3 Link – Unit 2 Notes(Will be updated soon) Unit 4 Link – Unit 5 Link – Unit 6 Link – Old Material Links UNIT I INTRODUCTION Introduction to IC Technology – MOS, PMOS, NMOS, CMOS & BiCMOS,technologies- Oxidation, Lithography, Diffusion, Ion implantation, Metallisation, Encapsulation, Probe testing, Integrated Resistors and Capacitors,CMOS nanotechnology. Vlsi_lec-design VLSI-lec-1 UNIT II BASIC ELECTRICAL PROPERTIES Basic Electrical Properties of MOS and BiCMOS Circuits: Ids-Vds relationships, MOS transistor threshold Voltage, gm, gds, the figure of merit Co; Pass transistor, NMOS Inverter, Various pull-ups, CMOS Inverter analysis, and design, Bi-CMOS Inverters.

PART-A Basic MOS Technology Integrated circuits era, enhancement and depletion mode MOS transistors. NMOS fabrication. CMOS fabrication, Thermal aspects of processing, BiCMOS technology, production of E-beam masks.

Specific information of vlsi lab manual for 7th sem ece pdf vtu's within short time. Everything VTU _ 6th Sem - Download as PDF File (.pdf), Text file (.txt) or read Click here to get 6th sem ECE Satellite ECE VTU Notes Fundamentals of CMOS VLSI 7th sem sjbit notes and Power electronics Lab Manual for ECE (vtu). Neil Weste and K. Eshragian, ―Principles of CMOS VLSI Design: A System Perspective‖, Second Edition, Pearson Education (Asia) Pvt. Wayne, Wolf, ―Modern VLSI Design: System on Silicon‖ Prentice Hall PTR/Pearson Education, Second Edition, 1998. Douglas A Pucknell & Kamran Eshragian, ―Basic VLSI Design‖ PHI 3rd.

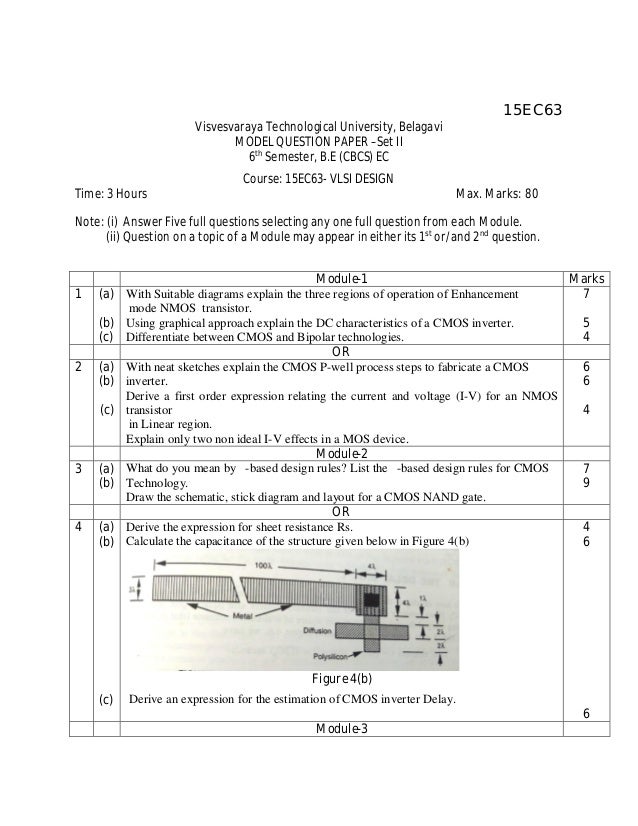

3 Hours MOS transistor theory Introduction, MOS device design equations. Tipovoj proekt stanciya lechebnogo gazosnabzheniya. Unit-2: Circuit Design Processes MOS layers, stick diagrams, Design rules, and layout- lambda-based design and other rules.

Examples, layout diagrams, symbolic diagram, tutorial exercises. Basic physical design of simple logic gates. Unit 3: CMOS Logic Structures CMOS complementary logic, BiCMOS logic, Pseudo-nMOS logic, Dynamic CMOS logic, clocked CMOS logic, Pass transistor logic, CMOS domino logic cascaded voltage switch logic (CVSL). Unit-4: Basic circuit concepts Sheet resistance, area capacitances, capacitances calculations. The delay unit, inverter delays, driving capacitive loads, propagation delays, wiring capacitance Scaling of MOS circuits Scaling models and factors, limits on scaling, limits due to current density and noise. PART-B Unit-5: CMOS subsystem design Architectural issues, switch logic, gate logic, design examples-combinational logic, clocked circuits. Other system considerations.

3 Hours Clocking strategies Unit-6: CMOS subsystem design processes General considerations, process illustration, ALU subsystem, adders, multipliers. Unit-7: Memory registers and clock Timing considerations, memory elements, memory cell arrays Unit-8: Testability Performance parameters, layout issues I/O pads, real estate, system delays, ground rules for design, test, and testability.